6.1. Розробка мікропроцесорної системи на основі мікроконтролера

6.1.1. Основні етапи розробки

МПС на основі МК використовуються частіше за все як вбудовані системи для вирішення задач управління деяким об'єктом. Важливою особливістю даного використання є робота в реальному часі, тобто забезпечення реакції на зовнішні події протягом певного тимчасового інтервалу. Такі пристрої одержали назву контролерів.

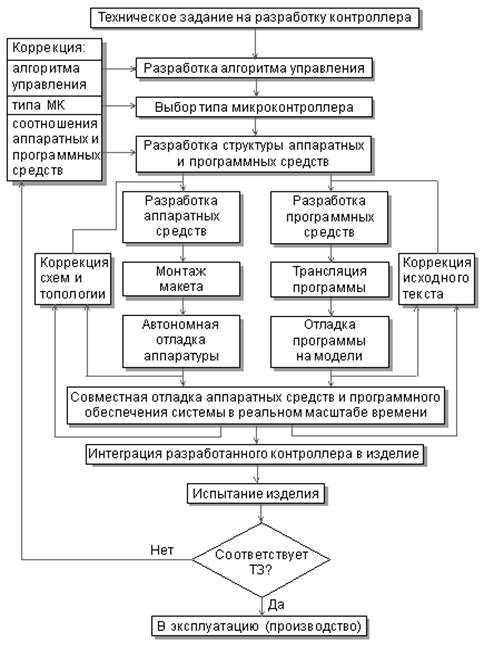

Технологія проектування контролерів на базі МК повністю відповідає принципу нерозривного проектування і відладки апаратних і програмних засобів, прийнятому в мікропроцесорній техніці. Це означає, що перед розробником такого роду МПС стоїть задача реалізації повного циклу проектування, починаючи від розробки алгоритму функціонування і закінчуючи комплексними випробуваннями у складі виробу, а, можливо, і супроводом при виробництві. Методологія проектування контролерів, що склалася до теперішнього часу, може бути представлена так, як показано на мал. 6.1.

В технічному завданні формулюються вимоги до контролера з погляду реалізації певної функції управління. Технічне завдання включає набір вимог, який визначає, що користувач хоче від контролера і прилад, що розробляється, повинен робити. Технічне завдання може мати вид текстового опису, і не містити в загальному випадку внутрішніх суперечностей.

На підставі вимог користувача складається функціональна специфікація, яка визначає функції, виконувані контролером для користувача після завершення проектування, уточнюючи тим самим, наскільки пристрій відповідає вимогам, що пред'являються. Вона включає описи форматів даних, як на вході, так і на виході, а також зовнішні умови, що управляють діями контролера.

Функціональна специфікація і вимоги користувача є критеріями оцінки функціонування контролера після завершення проектування. Може бути потрібно проведення декілька ітерацій, що включають обговорення вимог і функціональної специфікації з потенційними користувачами контролера, і відповідну корекцію вимог і специфікації. Вимоги до типу МК, що використовується, формулюються на даному етапі частіше всього в неявному вигляді.

Етап розробки алгоритму управління є найвідповідальнішим, оскільки помилки даного етапу звичайно виявляються тільки при випробуваннях закінченого виробу і приводять до необхідності дорогої переробки всього пристрою. Розробка алгоритму звичайно зводиться до вибору одного з декількох можливих варіантів алгоритмів, відмінних співвідношенням об'єму програмного забезпечення і апаратних засобів.

Мал. 6.1. Основні етапи розробки контролера.

При цьому необхідно виходити з того, що максимальне використовування апаратних засобів спрощує розробку і забезпечує високу швидкодію контролера в цілому, але супроводжується, як правило, збільшенням вартості і споживаної потужності. Зв'язано це з тим, що збільшення частки апаратних засобів досягається або шляхом вибору складнішого МК, або шляхом використовування спеціалізованих інтерфейсних схем. І те, і інше приводить до зростання вартості і енергоспоживання. Збільшення питомої ваги програмного забезпечення дозволяє скоротити число елементів контролера і вартість апаратних засобів, але це приводить до зниження швидкодії, збільшення необхідного об'єму внутрішньої пам'яті МК, збільшення термінів розробки і відладки програмного забезпечення. Критерієм вибору тут і далі є можливість максимальної реалізації заданих функцій програмними засобами при мінімальних апаратних витратах і за умови забезпечення заданих показників швидкодії і надійності в повному діапазоні умов експлуатації. Часто визначальними вимогами є можливість захисту інформації (програмного коду) контролера, необхідність забезпечення максимальної тривалості роботи в автономному режимі і інші. В результаті виконання цього етапу остаточно формулюються вимоги до параметрів МК, що використовується.

При виборі типа МК враховуються наступні основні характеристики:

- розрядність;

- швидкодія;

- набір команд і способів адресації;

- вимоги до джерела живлення і споживана потужність в різних режимах;

- об'їм ПЗП програм і ОЗП даних;

- можливості розширення пам'яті програм і даних;

- наявність і можливості периферійних пристроїв, включаючи засоби підтримки роботи в реальному часі (таймери, процесори подій і т.п.);

- можливість перепрограмування у складі пристрою;

- наявність і надійність засобів захисту внутрішньої інформації;

- можливість поставки в різних варіантах конструктивного виконання;

- вартість в різних варіантах виконання;

- наявність повної документації;

- наявність і доступність ефективних засобів програмування і відладки МК;

- кількість і доступність каналів поставки, можливість заміни виробами інших фірм.

Список цей не є вичерпним, оскільки специфіка проектованого пристрою може перенести акцент вимог на інші параметри МК. Визначаючими можуть виявитися, наприклад, вимоги до точності внутрішнього компаратора напруг або наявність великого числа вихідних каналів ШІМ.

Номенклатура МК, що випускаються в даний час, обчислюється тисячами типів виробів різних фірм. Сучасна стратегія модульного проектування забезпечує споживача різноманітністю моделей МК з одним і тим же процесорним ядром. Така структурна різноманітність відкриває перед розробником можливість вибору оптимального МК, що не має функціональної надмірності, що мінімізує вартість комплектуючих елементів.

Проте для реалізації на практиці можливості вибору оптимального МК необхідне достатньо глибоке опрацьовування алгоритму управління, оцінка об'єму виконуваної програми і числа ліній сполучення з об'єктом на етапі вибору МК. Допущені на даному етапі прорахунки можуть згодом привести до необхідності зміни моделі МК і повторної розводки друкарської плати макета контролера. В таких умовах доцільно виконувати попереднє моделювання основних елементів прикладної програми з використанням програмно-логічної моделі вибраного МК.

За відсутності МК, що забезпечує характеристики проектованого контролера, необхідне повернення до етапу розробки алгоритму управління і перегляд вибраного співвідношення між об'ємом програмного забезпечення і апаратних засобів. Відсутність відповідного МК всім вимогам означає, що для реалізації необхідного об'єму обчислень (алгоритмів управління) за відведений час потрібна додаткова апаратна підтримка. Негативний результат пошуку МК з необхідними характеристиками може бути пов'язаний також з необхідністю обслуговування великого числа об'єктів управління. В цьому випадку можливе використовування зовнішніх схем МК.

На етапі розробки структури контролера остаточно визначається склад апаратних модулів, підлягаючих розробці, протоколи обміну між модулями, типи роз'ємів. Виконується попереднє опрацьовування конструкції контролера. В частині програмного забезпечення визначаються склад і зв'язки програмних модулів, мова програмування. На цьому ж етапі здійснюється вибір засобів проектування і відладки.

Можливість перерозподілу функцій між апаратними і програмними засобами на даному етапі існує, але вона обмежена характеристиками вже вибраного МК. При цьому необхідно мати на увазі, що сучасні МК випускаються, як правило, серіями (сімействами) контролерів, сумісних програмно і конструктивно, але розрізняються по своїх можливостях (об'єм пам'яті, набір периферійних пристроїв і т.д.). Це дає можливість вибору структури контролера з метою пошуку самого оптимального варіанту реалізації.

Не можна не згадати тут про нову ідеологію розробки пристроїв на базі МК, запропонованою фірмою «Scenix». Вона заснована на використовуванні високошвидкісних RISC-мікроконтролерів серії SX з тактовою частотою до 100 Мгц. Ці МК мають мінімальний набір вбудованої периферії, а всі більш складні периферійні модулі емулюються програмними засобами. Такі модулі програмного забезпечення називаються «віртуальними периферійними пристроями», вони забезпечують зменшення числа елементів контролера, часу розробки, збільшують гнучкість виконання. До теперішнього часу розроблені цілі бібліотеки віртуальних пристроїв, що містять відладжені програмні модулі таких пристроїв як модулі ШіМ і ФАПЧ, послідовні інтерфейси, генератори і вимірники частоти, контролери переривань і багато інших.

6.1.2. Розробка і відладка апаратних засобів

Після розробки структури апаратних і програмних засобів подальша робота над контролером може бути распаралелена. Розробка апаратних засобів включає розробку загальної принципової схеми, розводку топології плати, монтаж макета і його автономну відладку. Час виконання цих етапів залежить від наявного набору апробованих функціонально-топологічних модулів, досвіду і кваліфікації розробника. На етапі введення принципової схеми і розробки топології використовуються, як правило, поширені системи проектування типа «ACCEL EDA» або «OrCad».

Автономна відладка апаратури на основі МК з відкритою архітектурою припускає контроль стану багаторозрядних магістралей адреси і даних з метою перевірки правильності звернення до зовнішніх ресурсів пам'яті і периферійних пристроїв. Закрита архітектура МК припускає реалізацію більшості функцій пристрою внутрішніми засобами мікроконтролера, що розробляється. Контролер, що розробляється, матиме мале число периферійних ІС, а обмін з ними йтиме переважно по послідовних інтерфейсах. Тут на перший план вийдуть питання узгодження по навантажувальній здатності паралельних портів МК і відладка алгоритмів обміну по послідовних каналах.

6.1.3. Розробка і відладка програмного забезпечення

Зміст етапів розробки програмного забезпечення, його трансляції і відладки на моделях істотно залежить від системних засобів, що використовуються. В даний час ресурси 8-розрядних МК достатні для підтримки програмування на мовах високого рівня. Це дозволяє використовувати всі переваги структурного програмування, розробляти програмне забезпечення з використанням роздільно трансльованих модулів. Одночасно продовжують широко використовуватися мови низького рівня типу асемблера, особливо при необхідності забезпечення контрольованих інтервалів часу. Задачі попередньої обробки даних часто вимагають використовування обчислень з плаваючою крапкою, трансцендентних функцій.

В даний час наймогутнішим засобом розробки програмного забезпечення для МК є інтегровані середовища розробки, що мають в своєму складі менеджер проектів, текстовий редактор і симулятор, а також допускаючі підключення компіляторів мов високого рівня типа Паскаль або Сі. При цьому необхідно мати на увазі, що архітектура багато яких з 8-розрядних МК унаслідок малої кількості ресурсів, сторінкового розподілу пам'яті, незручної індексної адресації і деяких інших архітектурних обмежень не забезпечує компілятору можливості генерувати ефективний код. Для обходу цих обмежень розробники ряду компіляторів були вимушені перекладати на користувача турботу про оптимізацію коду програми.

Для перевірки і відладки програмного забезпечення використовуються так звані програмні симулятори, надаючі користувачу можливість виконувати розроблену програму на програмно-логічній моделі МК. Програмні симулятори розповсюджуються, як правило, безкоштовно і конфігуровані відразу на декілька МК одного сімейства. Вибір конкретного типа МК серед моделей сімейства забезпечує відповідна опція меню конфігурації симулятора. При цьому моделюється робота ЦП, всіх портів вводу/виводу, переривань і іншої периферії. Карта пам'яті модельованого МК завантажується в симулятор автоматично, відладка ведеться в символьних позначеннях регістрів.

Завантаживши програму в симулятор, користувач має нагоду запускати її в покроковому або безперервному режимах, задавати умовні або безумовні точки зупинки, контролювати і вільно модифікувати вміст елементів пам'яті і регістрів симульованого МК.

6.1.4. Методи і засоби сумісної відладки апаратних і програмних засобів

Етап сумісної відладки апаратних і програмних засобів в реальному масштабі часу є самим трудомістким і вимагає використовування інструментальних засобів відладки. До числа основних інструментальних засобів відладки відносяться:

- внутрішньосхемні емулятори;

- платня розвитку (оцінна платня);

- монітори відладки;

- емулятори ПЗП.

Внутрішньосхемний емулятор - програмно-апаратний засіб, здатний замінити емульований МК в реальній схемі. Стиковка внутрішньосхемного емулятора з відладжуваною системою проводиться за допомогою кабелю із спеціальною емуляційною головкою, яка вставляється замість МК у відладжувану систему. Якщо МК не можна видалити з відладжуваної системи, то використовування емулятора можливе, тільки якщо цей мікроконтролер має налагоджувальний режим, при якому всі його виводи знаходяться в третьому стані. В цьому випадку для підключення емулятора використовують спеціальний адаптер-кліпсу, який підключається безпосередньо до виводів емульованого МК.

Внутрішньосхемний емулятор - цей наймогутніший і універсальний налагоджувальний засіб, який робить процес функціонування відладжуваного контролера прозорим, тобто легко контрольованим, довільно керованим і модифікованим.

Плата розвитку (макетна), або, як прийнято її називати в зарубіжній літературі, оцінна плата (Evaluation Boards), є свого роду конструкторами для макетування електронних пристроїв. Звичайно це друкарська плата зі встановленим на ній МК і всією необхідною йому стандартною периферією. На цій платі також встановлюють схеми зв'язку із зовнішнім комп'ютером. Як правило, там же є вільне поле для монтажу прикладних схем користувача. Іноді передбачена вже готова розводка для установки додаткових пристроїв, що рекомендуються фірмою. Наприклад, ПЗП, ОЗП, рідкокристалічний дисплей, клавіатура, АЦП і ін. Окрім учбових або макетних цілей, такі допрацьовані користувачем плати можна використовувати як одноплатні контролери, вбудовувані в малосерійну продукцію.

Для більшої зручності плати розвитку комплектуються ще і найпростішим засобом відладки на базі монітора відладки. Використовуються два типи моніторів відладки: один для МК, мають зовнішню шину, а другий - для МК, що не мають зовнішньої шини.

В першому випадку налагоджувальний монітор поставляється у вигляді мікросхеми ПЗП, яка вставляється в спеціальну розетку на платі розвитку. Плата також має ОЗП для програм користувача і канал зв'язку із зовнішнім комп'ютером або терміналом. В другому випадку плата розвитку має вбудовані схеми програмування внутрішнього ПЗП МК, які управляються від зовнішнього комп'ютера. При цьому програма монітора просто заноситься в ПЗП МК спільно з прикладними кодами користувача. Прикладна програма повинна бути спеціально підготовлена: в потрібні місця необхідно вставити виклики налагоджувальних підпрограм монітора. Потім здійснюється пробний прогін. Щоб внести в програму виправлення, користувачу треба стерти ПЗП і провести повторний запис. Готову прикладну програму одержують з відладженої шляхом видалення всіх викликів моніторних функцій і самого монітора відладки. Можливості відладки, що надаються комплектом «плата розвитку плюс монітор», не такі універсальні, як можливості внутрішньосхемного емулятора, та і деяка частина ресурсів МК в процесі відладки відбирається для роботи монітора. Проте, наявність набору готових програмно-апаратних засобів, що дозволяють без втрати часу приступити до монтажу і відладки проектованої системи, у багатьох випадках є вирішальним чинником. Особливо якщо врахувати, що вартість такого комплекту дещо менше ніж вартість більш універсального емулятора.

Емулятор ПЗП - програмно-апаратний засіб, що дозволяє заміщати ПЗП на відладжуваній платі, і підставляюче замість нього ОЗП, в яке може бути завантажена програма з комп'ютера через один із стандартних каналів зв'язку. Цей пристрій дозволяє користувачу уникнути багатократних циклів перепрограмування ПЗП. Емулятор ПЗП потрібен тільки для МК, які можуть звертатися до зовнішньої пам'яті програм. Цей пристрій прирівняний по складності і за вартістю з платою розвитку і має одну велику перевагу: універсальність. Емулятор ПЗП може працювати з будь-якими типами МК.

Емульована пам'ять доступна для перегляду і модифікації, але контроль над внутрішніми управляючими регістрами МК був до недавнього часу неможливий.

Останнім часом з'явилися моделі інтелектуальних емуляторів ПЗП, які дозволяють «заглядати» всередину МК на плати користувача. Інтелектуальні емулятори є гібридом із звичайного емулятора ПЗП, монітора відладки і схем швидкого перемикання шини з одного на іншій. Це створює ефект, неначебто монітор відладки був встановлений на платі користувача і при цьому він не займає у МК ніяких апаратних ресурсів, окрім невеликої зони програмних кроків, приблизно 4К.

Етап сумісної відладки апаратних і програмних засобів в реальному масштабі часу завершується, коли апаратура і програмне забезпечення спільно забезпечують виконання всіх кроків алгоритму роботи системи. В кінці етапу відладжена програма заноситься за допомогою програматора в енергонезалежну пам'ять МК, і перевіряється робота контролера без емулятора. При цьому використовуються лабораторні джерела живлення. Частина зовнішніх джерел сигналів може моделюватися.

Етап інтеграції розробленого контролера у виріб полягає в повторенні робіт по сумісній відладці апаратури і управляючої програми, але при роботі у складі виробу, живленні від штатного джерела і з інформацією від штатних джерел сигналів і датчиків.